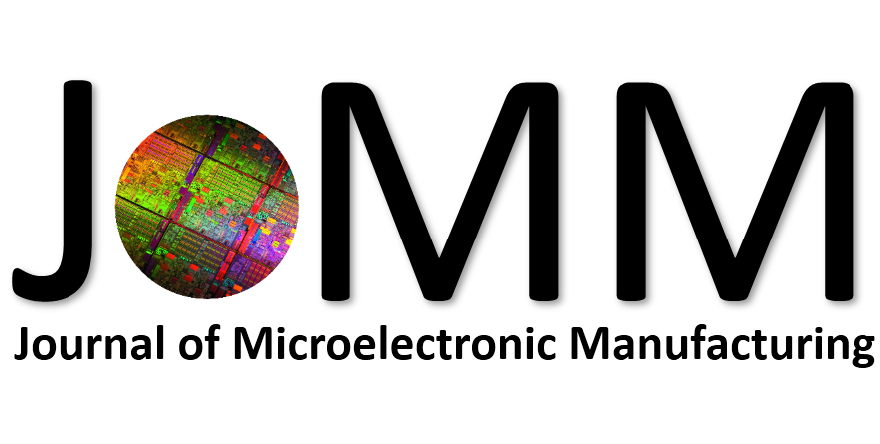

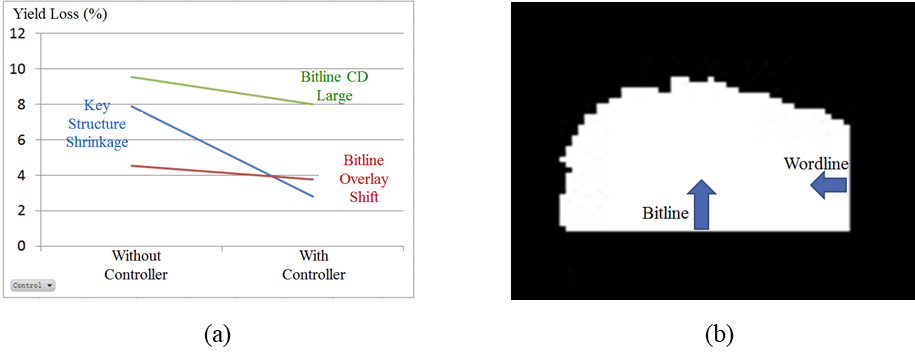

In general, during semiconductor manufacturing process engineers will send wafers to perform various types of test. One of the key purposes of these tests is to achieve key information such as CD (critical dimension) of important structures or devices. And then based on CD information engineers are able to setup R2R control for feedback or feed-forward process control. However, due to complexity of the some device structure and corresponding effect, it is difficult for engineers to conduct accurate prediction of yield impact based on structure CD or overlay fluctuation data. One typical example of this type of structure is contact area in a deep hole. One example of this situation is indicated in Figure 1. B (in gray) is base material. The contact area C (in red) is surrounded by much higher structure A (in green) and planned to have direct contact with D (in yellow).

Figure 1.

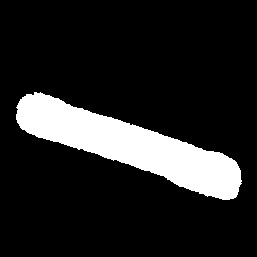

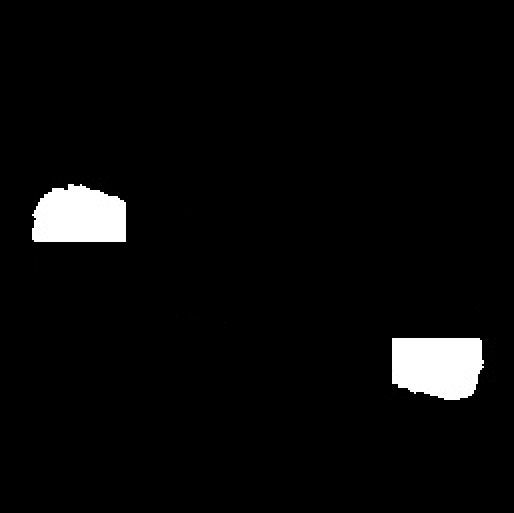

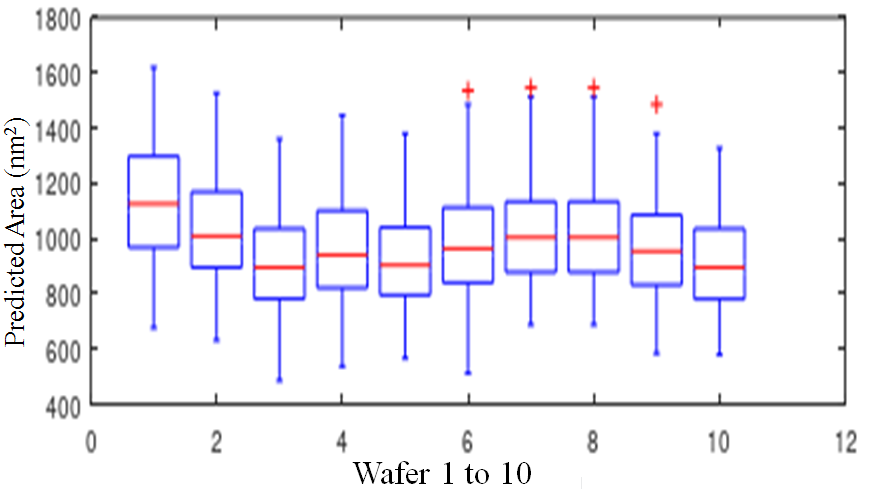

(a) Contact hole structure before contact material D deposited; (b) contact hole structure after contact material D deposited. The size of contact area has direct impact to contact resistance. Small contact area will result in high contact resistance and result in device malfunction. Due to complexity of manufacturing process, engineers can only get crutial information during the beginning of the process. After surrounding structure stacked, the hole remained to setup electrical contact is too deep to make a measurement based on current measurement instrument technology. Figure 2 shows the measurement result for this type of structure. Besides, due to the contact area is completely unseen, any CD or overlay shifting when surrounding top structure built is difficult for engineer to judge the effect.

Figure 2.

Measurement instrument cannot take clear view of contact area in the deep hole. This paper proposed a novel type of R2R control strategy as a practical solution to this type of issue. R2R control has been widely used in semiconductor manufacturing industry. The R2R control is commonly based on measuring instrument result. To optimize the control strategy, researchers have tried various types of control algorithm, such as EWMA

[1, dEWMA

[2]. And in the past 20 years, with popularity of VM (virtual metrology) and the rise of machine learning technology, many more engineers and researchers start to conduct a control strategy based on virtual measurement

[3][4][5][6]. However, these new strategies are all focus on information prediction based on equipment sensor data which requires huge data pool and high accuracy of the algorithm.

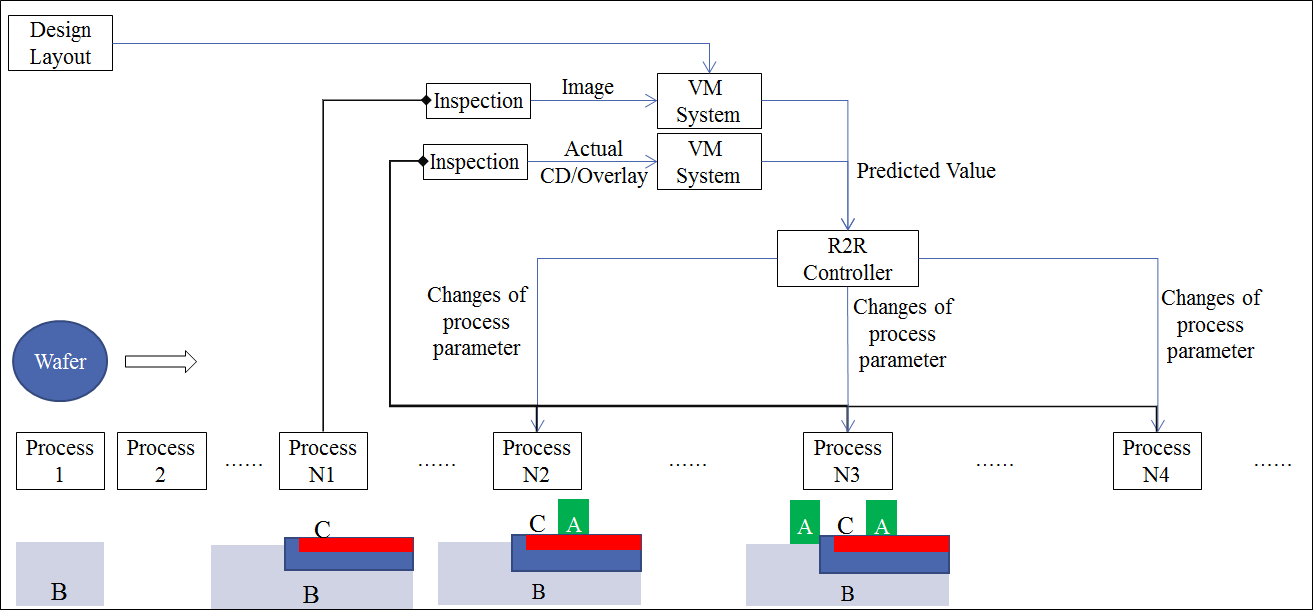

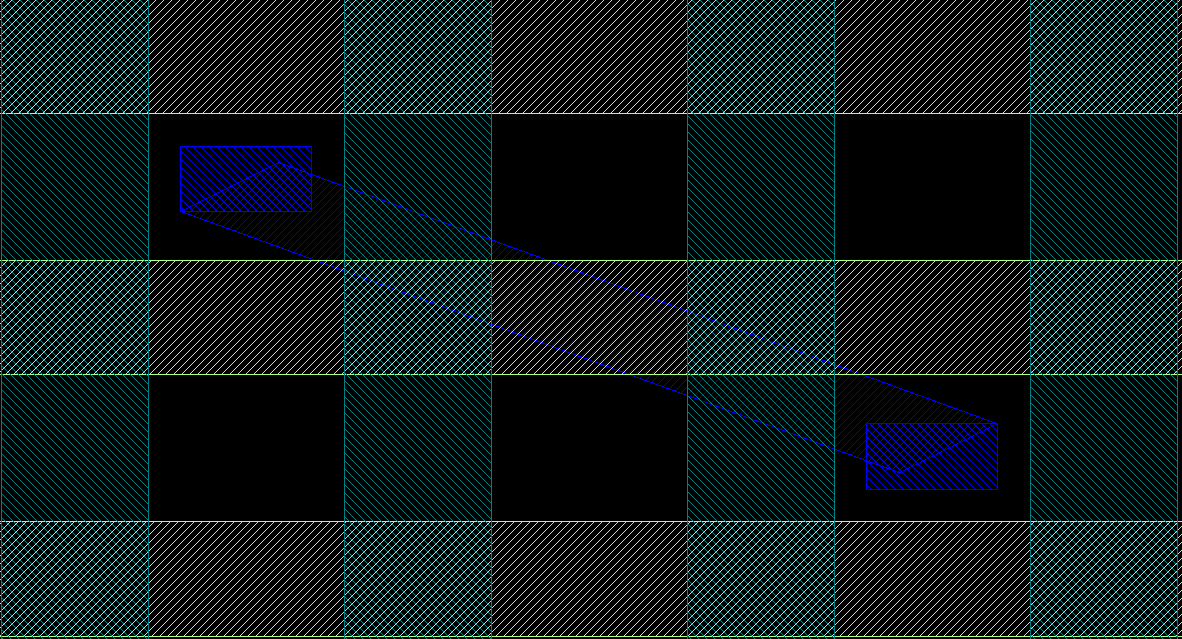

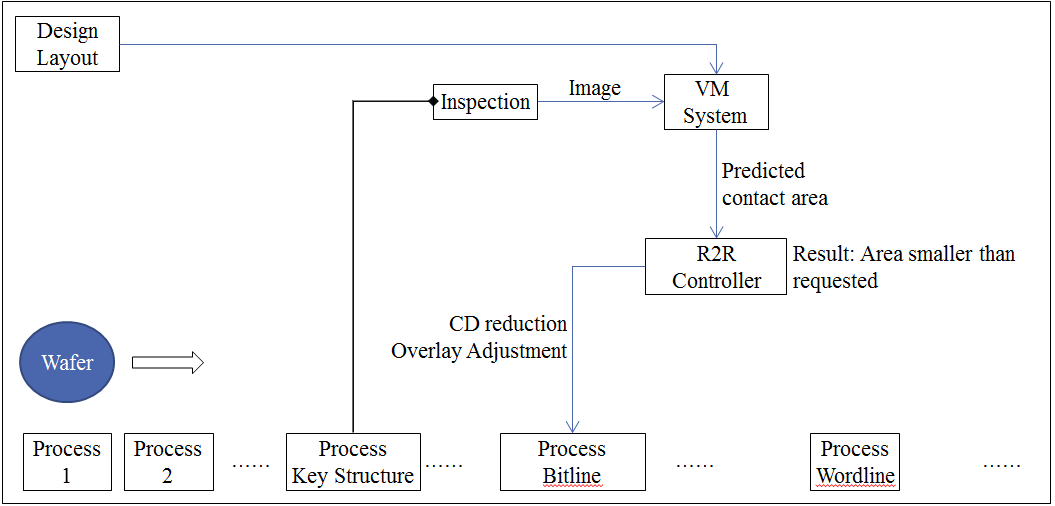

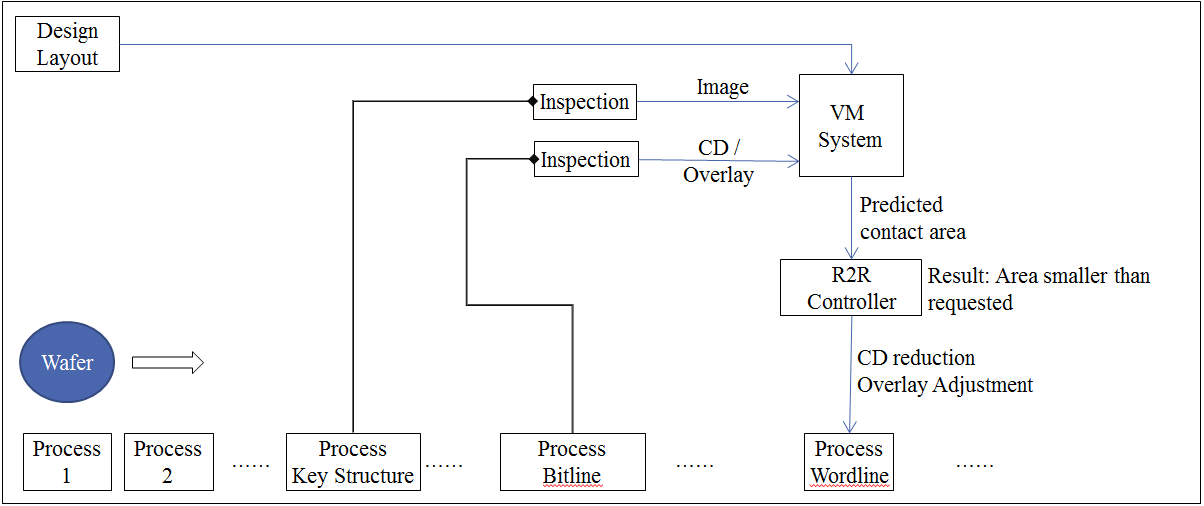

This paper proposed completely different concept of VM. The new type of R2R control strategy is illustrated in Figure 3 below. The VM system will utilize structure information obtained from circuit design document. Based on layout dimension VM system can virtually deploy structure on the inspection image and then generate a new type of virtually measurement data. Associated with new type of metrology data input, a novel feed-forward rolling-wave R2R control plan is formed. Once initial predicted value input, the R2R controller can commend all related subsequent process steps to change process parameter in order to achieve target value. And after subsequent process completed with inspection information (such as CD, overlay), VM system can update the real structure location and then update the R2R controller the latest predicted value. Based on latest predicted value, the R2R controller can re-calculate and send newest process parameter control instruction to the rest of process steps.

Figure 3.

The diagram of new R2R control strategy.