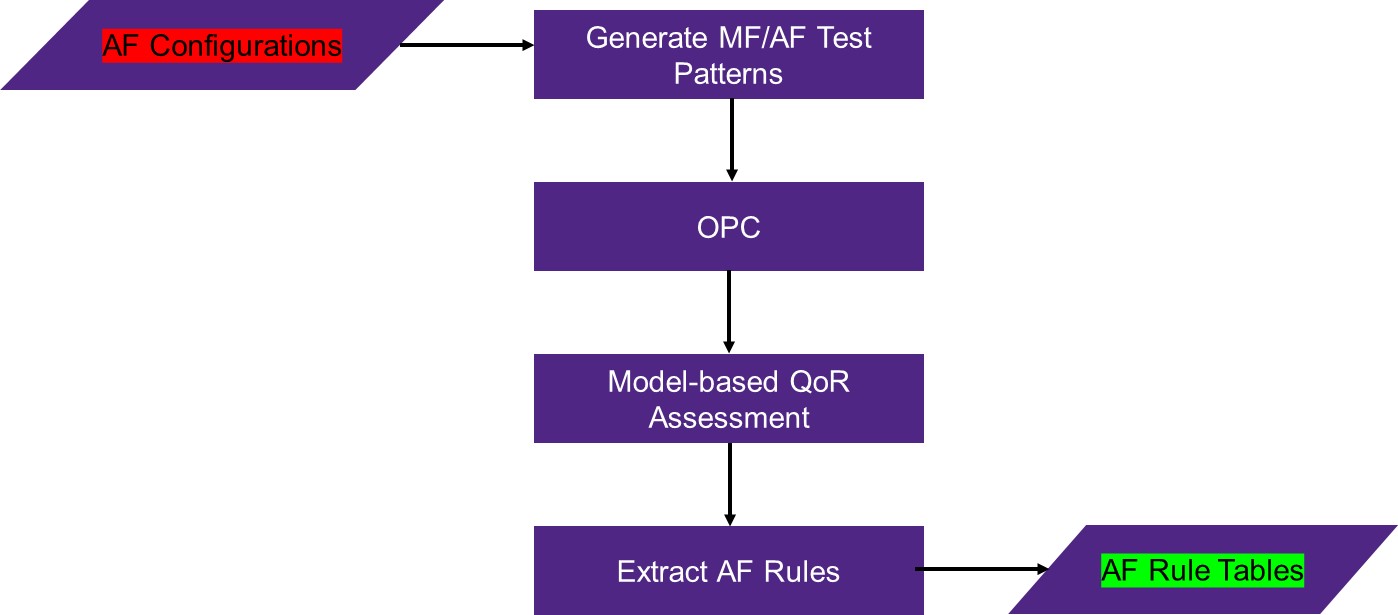

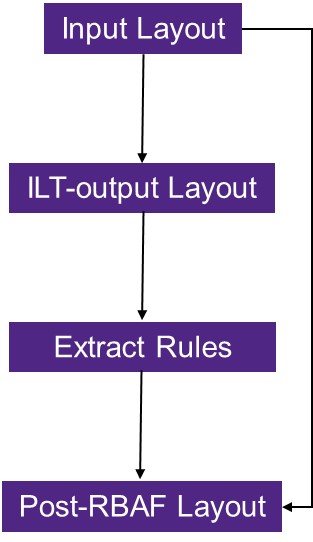

As discussed in the previous section, the rule-based assist features are well received due to their mask synthesis performance and consistency. There have been studies years before to propose the hybrid assist feature implementation methodology by using process window models to select assist feature rules [1]. There are still rooms to improve by automating such evaluating processes. To speed-up the rule table generation process, the model-assisted rule tables are offered in this paper. Figure 1 shows the general flow of MART. After the main feature test patterns are generated, there are different configurations to insert the assist features. OPC is then applied on these test patterns with assist features. Next, a process window model is used to evaluate the quality of different assist feature configurations. Finally, based on the results, the best assist feature configurations will be produced.

Compared with the traditional rule table exaction process, the key point here is that the mask-making, wafer-printing and data measurements are all replaced by lithographic simulations. This approach significantly improves the turn-around-time and efficiency evaluating assist feature configurations and rules.

Figure 1.

Data flow for MART - inputs are shown in red, outputs are shown in green (MF: main feature, AF: assist feature). For 1D assist features, the rule table is relatively simple. The user only needs to specify the assist feature width and the distance between main feature and assist feature or between assist feature and assist feature.

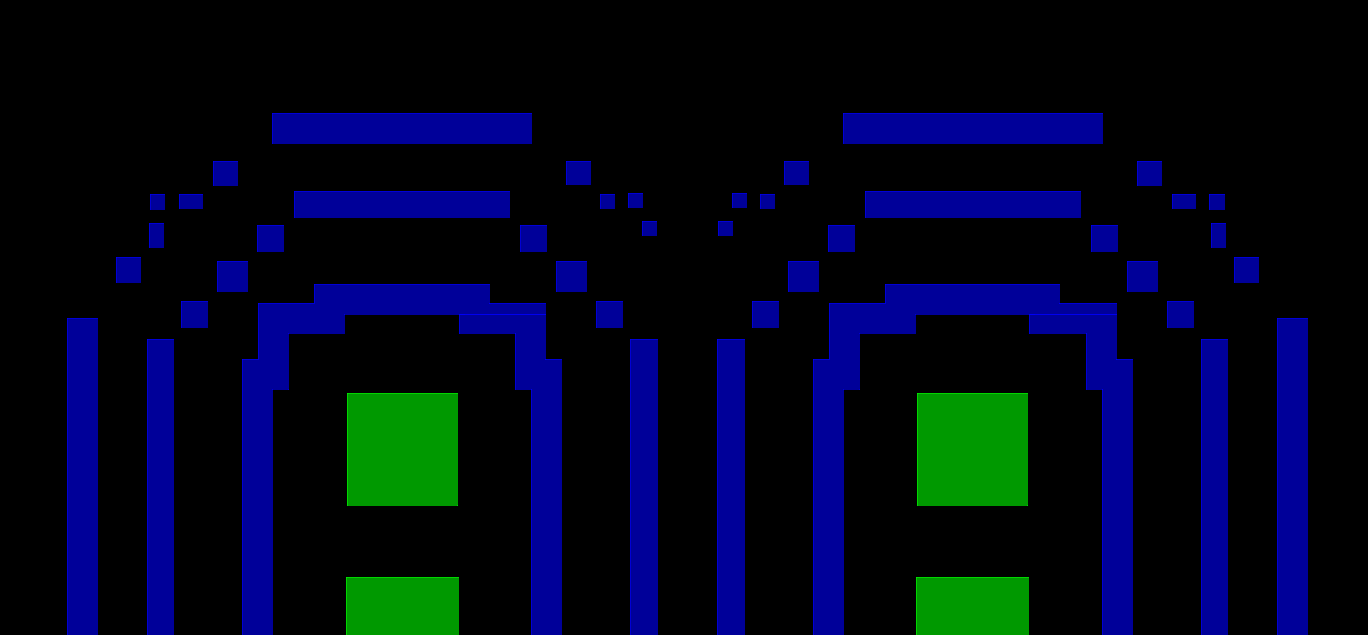

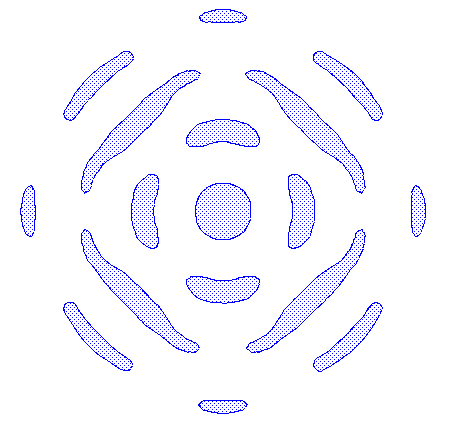

For 2D assist features, the rule table is much more complicated. A third dimensional parameter is introduced which defines the angle of the assist feature relative to the main feature. Figure 2 shows a typical layout with 2D assist feature placement. The definition of such rule is much more complicated than the 1D assist feature rule table. Under the 2D scenario, the model-assisted approach shows even bigger advantages by automating the process to select the best 2D assist feature rule tables.

Figure 2.

A typical layout with 2D assist feature placment 3. Process Window Evaluation of Different 2D Assist Feature Types

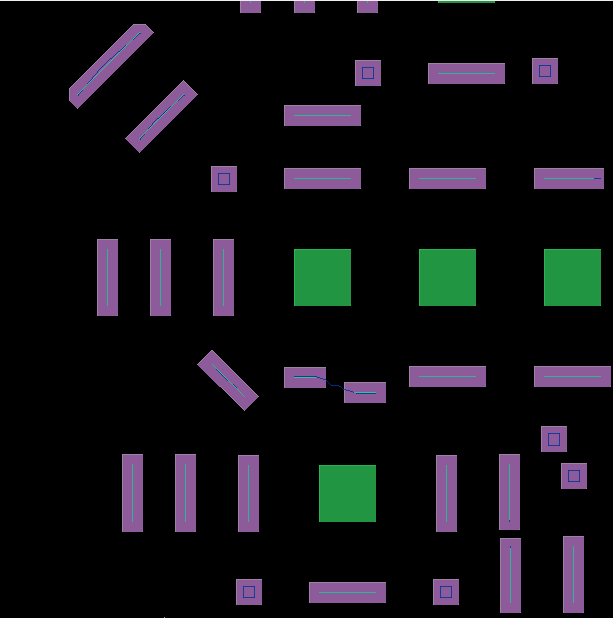

There are many choices influencing the final 2D assist feature placement on the Manhattan skeleton. For example, the assist features may be connected or disconnected, they may be Manhattan only, and Manhattan only assist features may enforced mask rule checks (MRC).

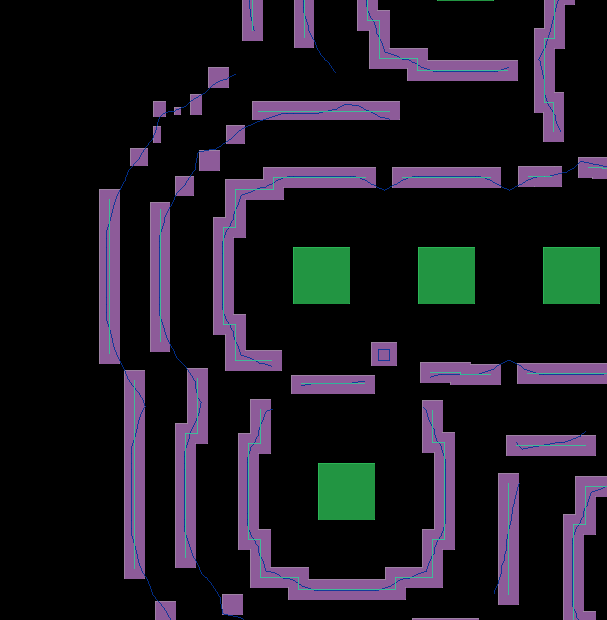

To evaluate the impact of the different assist feature options, we run the post-OPC lithography rule checks, and measure the process variation band as the success criteria of the assist feature placement. The experiment is based on a 193nm immersion lithography process for a contact layer with the target CD of 90nm. Figure 3 shows the different 2D assist feature placement options that were tested, from the manual 2D placement to the MART2D with enforced MRC.

Table 1 provides the process variations that were extracted for each of the different placement options. The minimum and maximum CD metrics are the respective lower and upper CD values across the process windows, reported as a percentage of target CD. A smaller absolute value means a better CD control through process window.

From the test data, it is found that the process window improvement is not sensitive to the assist feature shapes. Some arbitrary changes in the assist feature shapes may even degrade the process window metrics. What is more important is the assist feature placement rules themselves. MART2D offers a good way to find such rules. The data shows that the best solution is obtained from MART2D with enforced MRC to filter out some unwanted small shapes. Such a methodology provides the smallest CD variation range through the process window.

Figure 3.

Different 2D assist feature placement candidates: (a) Manual 2D assist feature placment, 45 degree only, (b) All angle disconnected 2D assist feature placement, (c) All angle connected 2D assist feature placement, (d) Manhattan only 2D assist feature placment, (e) MART2D assist feature placement, without MRC, and (f) MART2D assist feature placment, MRC enforced. Table 1.

Comparisons with different 2D assist feature placement methodology | Scenarios | Minimum CD (%) | Maximum CD (%) | Range (%) |

| a) Manual, 45 degree only | -15.58 | 17.68 | 33.26 |

| b) Manual, All-angle disconnected | -18.38 | 18.76 | 37.14 |

| c) Manual, All-angle connected | -17.76 | 19.20 | 36.96 |

| d) Manual, Manhattan only | -17.99 | 19.21 | 37.21 |

| e) MART2D | -13.99 | 16.91 | 30.90 |

| f) MART2D+MRC | -13.98 | 16.89 | 30.87 |