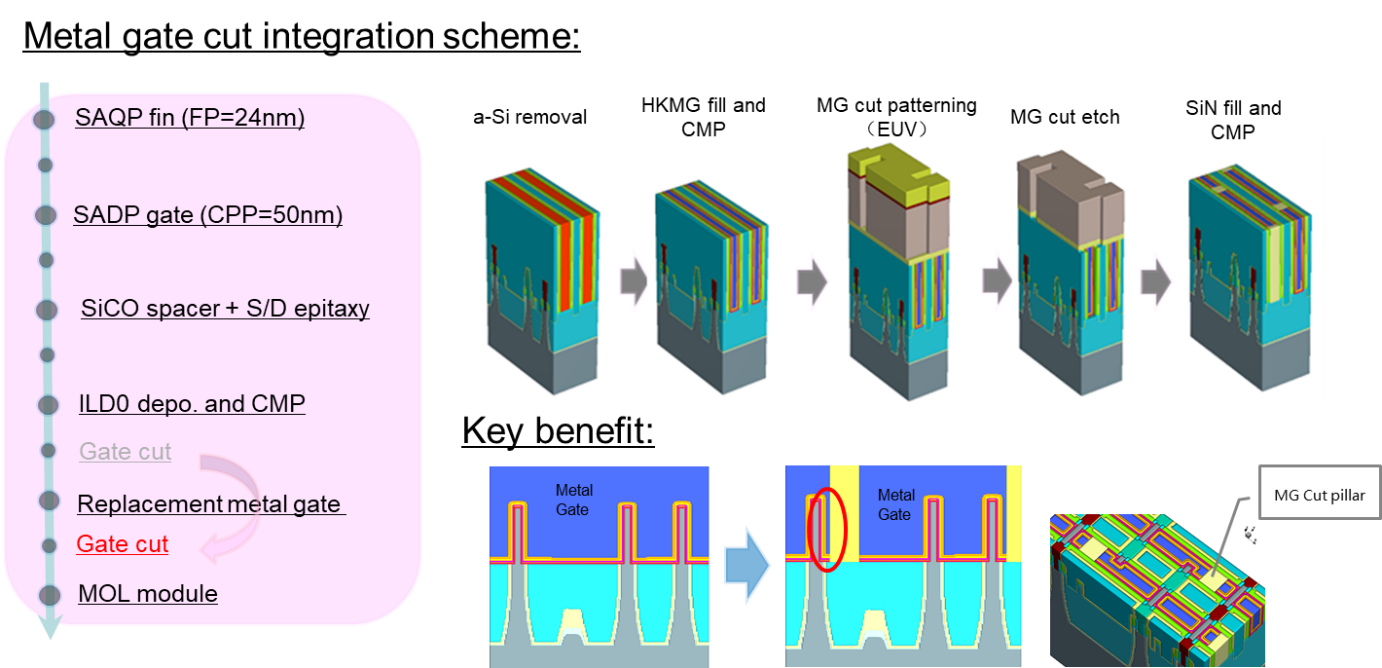

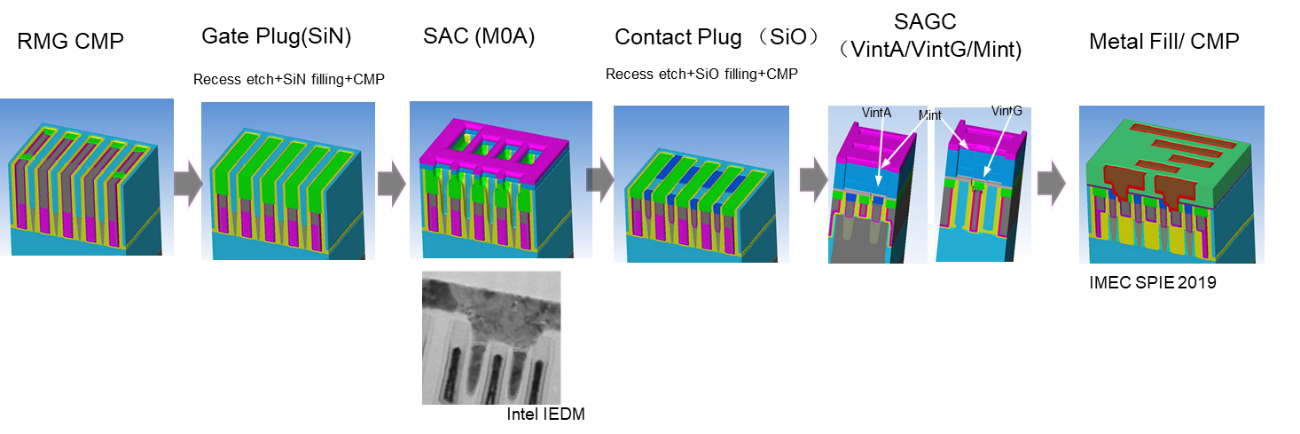

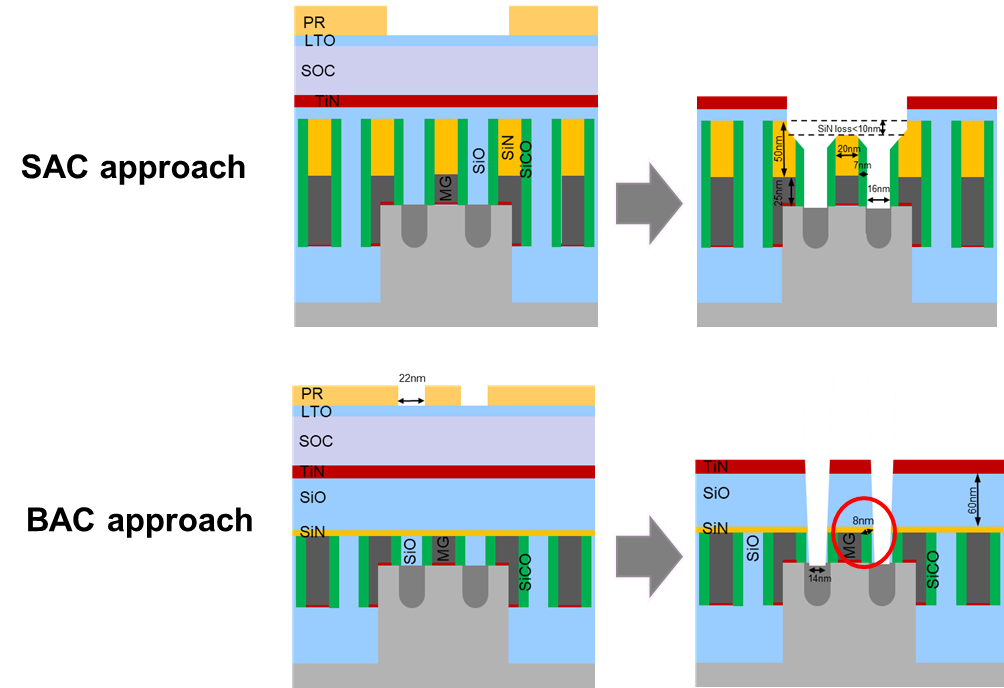

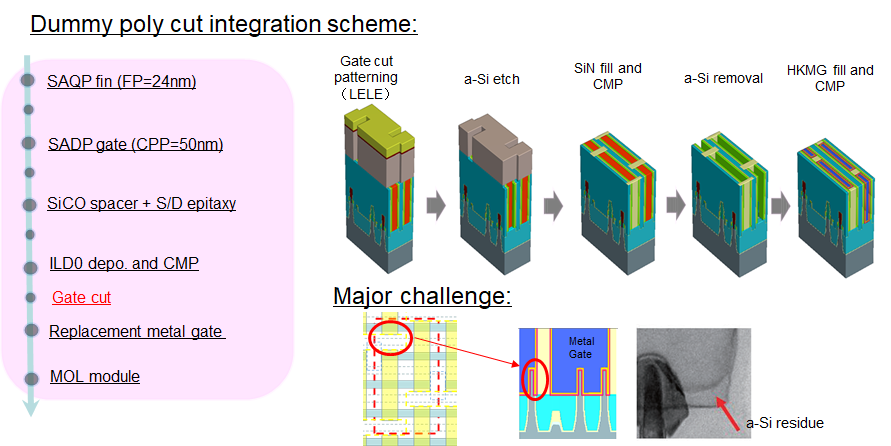

In order to reduce lithography process challenge, i.e., overlay window can be enlarged significantly by using the oversized contact mask, Self-aligned contact (SAC) approach is widely adopted to realize complex contact pattern. Figure 4 is the MOL contact patterning process flow schematics with SAC approach which is cited from IMEC SPIE paper [4]. In this process integration, the first step is to form the source/drain contact with SAC oxide etch which needs high etch selectivity to the gate plug (GP) (Si3N4) and the sidewall spacer (SiCO). The second step is called self-aligned gate contact (SAGC) which needs two separate SAC etch to form contact holes (VintG) connecting the first metal (Mint) to the gate and contact holes ( VintA) connecting Mint to source/drain contact respectively. Both of the SAC etch processes also need high selectivity.

Figure 4.

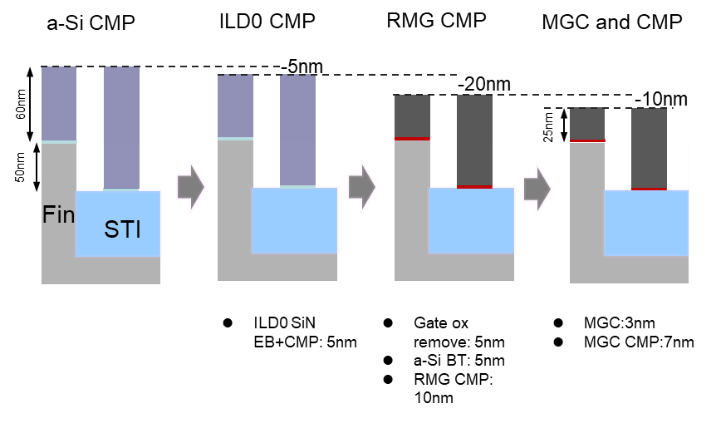

MOL contact process flow schematics with SAC approach. SAC approach is used to shift patterning challenge from lithography to dry etch process with high etch selectivity. It is an important booster for device scaling with 193 nm immersion lithography. But the process flow is very complicated including repetitive recess etch, plug materials filling (Si3N4 for gate plug, SiO2 for contact plug) and CMP steps. The challenge of process quality control will be very large such as film thickness uniformity. Furthermore, all of these processes will consume the gate height step by step, and eventually lead to the initial gate height will be very high. Figure 5 shows gate height loss assumptions with SAC approach. The initial gate height will be about 165 nm on STI, considering the Si3N4 and SiO2 hard-mask thickness atop the α-Si before gate etch, the actual HAR will reach 9 with 32 nm gate space. This will aggravate process difficulty for subsequent etch and gap fill processes from dummy poly gate patterning.

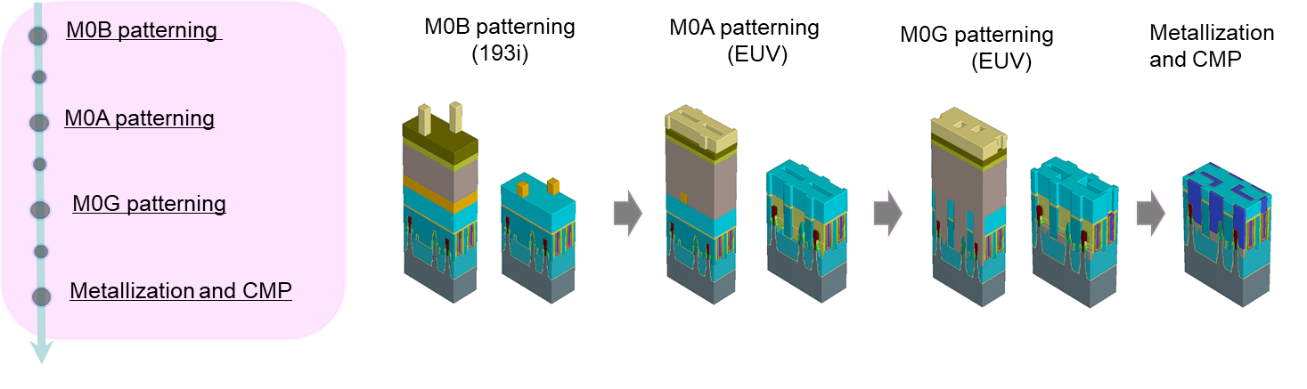

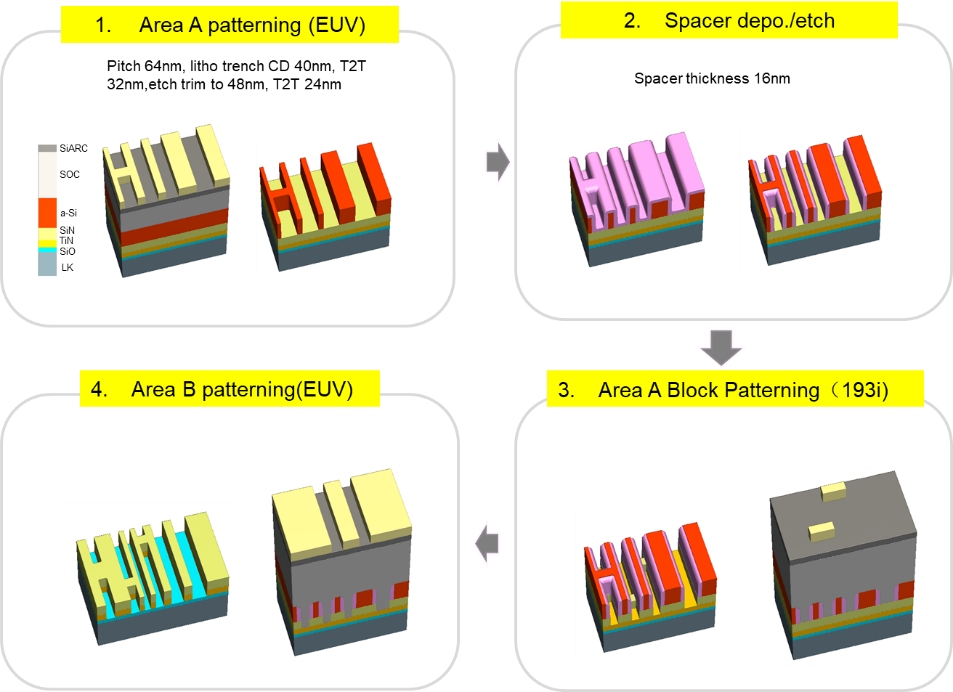

With EUV lithography, brutal-aligned-contact (BAC) can be realized for 5 nm node technology. According to 5 nm design rule, the contact pitch is about 50 nm and minimal trench CD (critical dimension) is 14 nm. 3 lithography exposures are required to realize the contact pattern, two is for the S/D contact patterning (one 193 nm immersion lithography for the S/D contact block (M0B), one EUV lithography for the S/D contact final patterning), and one is for the gate contact patterning. The BAC approach process flow is shown in Figure 6.

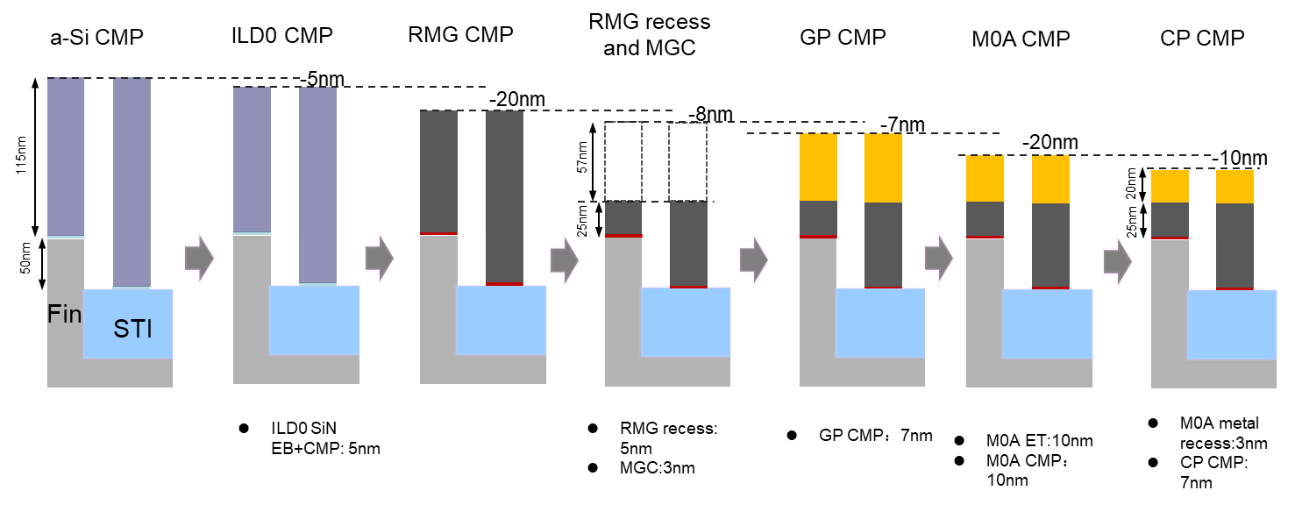

From the BAC process flow schematics, we can see the process is simplified with fewer process steps. It will help to reduce process variation and enhance process control. The gate height loss assumptions with BAC approach is shown in Figure 7. The initial gate height will be reduced to about 110 nm on STI, and the HAR is ~6.5 when the gate space is 32 nm including Si3N4 and SiO2 HM before gate etch. The HAR is reduced by nearly 30% compared to the previous SAC approach.

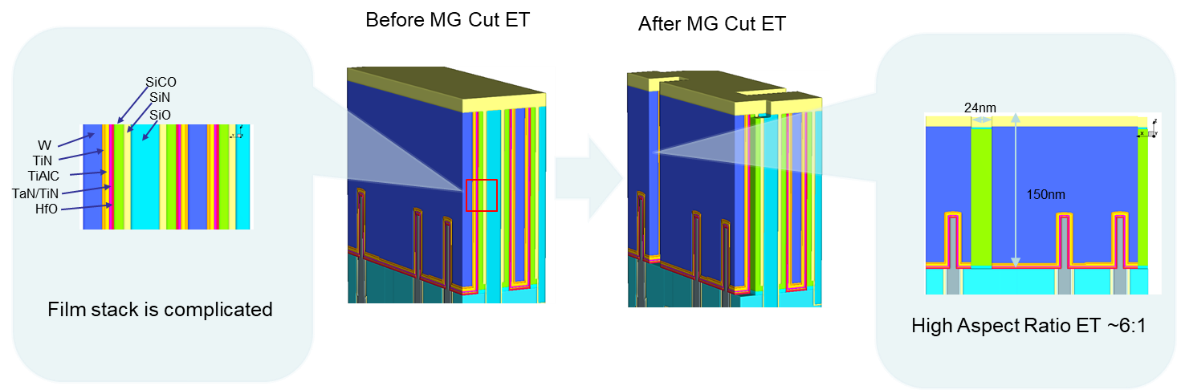

Figure 5.

Gate height loss assumptions with SAC approach. Figure 6.

Brutal-Aligned-Contact (BAC) approach. Figure 7.

Gate height loss assumptions with BAC approach. For contact process, the isolation space thickness variation between contact and gate is the key parameter related to the failure of devices. We also checked the EPE (Edge placement error) window which schematics is shown in Figure 8. For SAC approach, there is no EPE window concern because the S/D contact trench position is defined by self-aligned process, and high selectivity etch ensure the isolation spacer loss is very low. But for BAC approach, the process weak point is at the top of isolation spacer, the isolation space is about 8 nm and the isolation space variation 3-sigma is about 3.5 nm with stringent process control (major specifications as: EUV overlay≤2.5 nm, LER≤1.5 nm). Under this condition, the minimal safe dielectric isolation space 4 nm can be guaranteed.

Figure 8.

Isolation space EPE window check SAC & BAC.

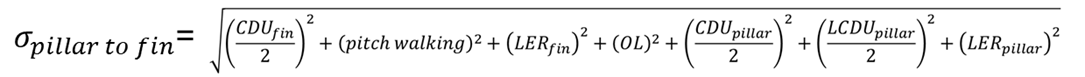

(1)

(1)