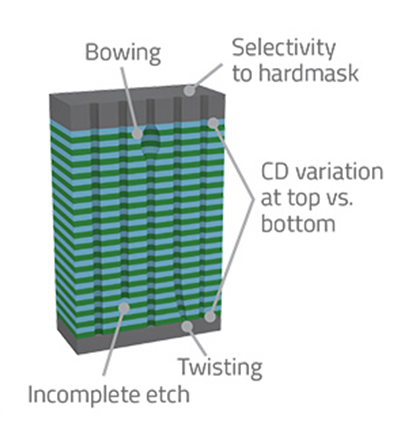

Continued manufacturing process improvements are essential in delivering memory devices with higher I/O performance, higher bit density, and at lower cost. Current 3D NAND technology involves process steps that form array and peripheral CMOS (Complementary Metal-Oxide-Semiconductor) regions side-by-side, resulting in waste of silicon real estate thermal budget deficit and film stress compromises, thus limits the paths of making advanced 3D NAND devices. An innovative architecture was invented to overcome these challenges by connecting two wafers electrically face-to-face through metal VIAs (Vertical Interconnect Access).

Traditional approach to connecting wafers is by using VIA, but metal in the VIA exhibits higher coefficient of thermal expansion (CTE) compared to silicon and dielectrics in the wafer, and this induces large stresses in both the metal plugs and the surrounding silicon. The large thermo-mechanical stress can be mitigated by proper CMP (Chemical Mechanical Planarization) process. In a study of a CMP process resulting in VIA shape that is slightly protruding on the top wafer and slightly dishing in the bottom wafer, thus allowing for necessary wafer to wafer overlay bonding tolerance, better overall resistivity and yield were achieved [4].

Wafer bonding, as a 3D integration technology, provides a new paradigm to vertically integrate various building blocks. Not only can it shorten wires with smaller chip sizes, but also it is a new technology platform for heterogeneous integration by stacking and connecting dissimilar materials or different modules on one substrate. Today, the pre-bonding wafer-to-wafer alignment accuracy can be achieved on the order of 0.25 μm using commercially available wafer-to-wafer alignment tools [5, 6]. However, the process related misalignment has yet to be thoroughly studied, while it becomes more significant.

Highly accurate and efficient metrology is required to monitor interface processing and wafer connecting procedures due to increased process complexity and precision requirements. Universal metrology and measurement techniques are applied here include ellipsometry for thin film thickness and corresponding wafer-wide variation, SEM for VIA critical dimensions, AFM for interface roughness, profilometry for interface topography and IR transmission microscopy for bonding misalignment. Advanced metrology technologies have been developed for related processes controlling, however more insights must be given to solve systematic bottlenecks and meet the request of higher production throughput. Basically improvements are in dire need in two parts:

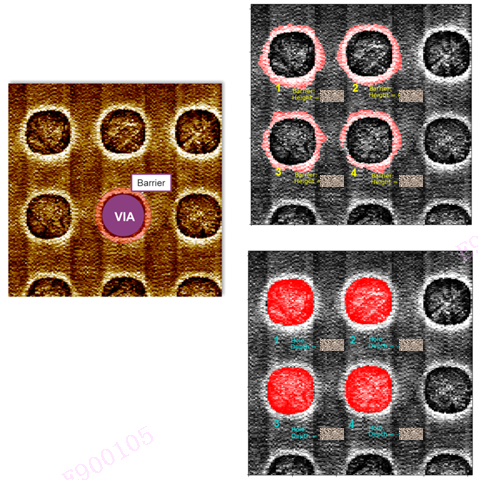

VIA Dishing -The VIA interface topography, which normally resembles a dishing shape to ensure connection between wafers, is one of the most important factors in determining the quality of wafer interconnection. A suitable monitoring scheme for VIA dishing is necessary to avoid structural and reliability issues such as interconnection open, metal void, metal diffusion, etc. The industry has developed several methods in the product development flow to proactively identify these hotspots, also known as weak points [7-9]. Despite all such design verification methods, we must still employ aggressive metrology methods to detect any deformation during fabrication [10, 11]. AFM appears to be the only reliable metrology method for this purpose. Yet it still poses two primary metrology challenges. Firstly, the shallow depth makes it difficult for capturing the edges of these VIA features on wafer. Frequent capturing failures happen when measuring VIA dishing because of the small average depth. Also, partial capturing and unwanted pixels exacerbate the difficulty in accurate measurement. Secondly, the dishing depth varies depending on metal volume and density distribution that is caused by chip layout, which leads to potential weak points. To address the problems, our previous work (Figure. 8) demonstrated the implementation of an inline metrology to precisely measure VIA location and its depth of dishing and protrusion, ensuring better CMP process control by utilizing pattern centric solution [12].

Figure 8.

(Left) original AFM data shows metal barrier around VIA; (right-top) barrier height and (right-bottom) dishing depth was automatically exported by the IDP application based on VIA sequence. Yet the long measurement duration severely limits the application of AFM in mass production [13]. Among height related measurement methods, WLI (White Light Interferometer) offers an alternative option. In brief, white light interferometer provides high precision by using optical phase-shifting techniques, and a broad spectral width light source is generally applied in order to increase dynamic range of measurement [13]. Although a vertical scanning is mandatory to collect interference fringes, the field data with less than 100 nm per pixel resolution is obtained spontaneously by WLI, which greatly reduces measurement duration. As a result, WLI is more than 100 times faster than line-scanning AFM in the same measurement. But multiple-layer reflection caused by transparent films stack has a large impact on the interference fringes since it shifts the wave phase and derives inauthentic height. For improvement, a spectrometer which measures spectrum with high precision at the reference location of the test surface can be added to a typical WLI optical system for pattern sample topography measurement [14].

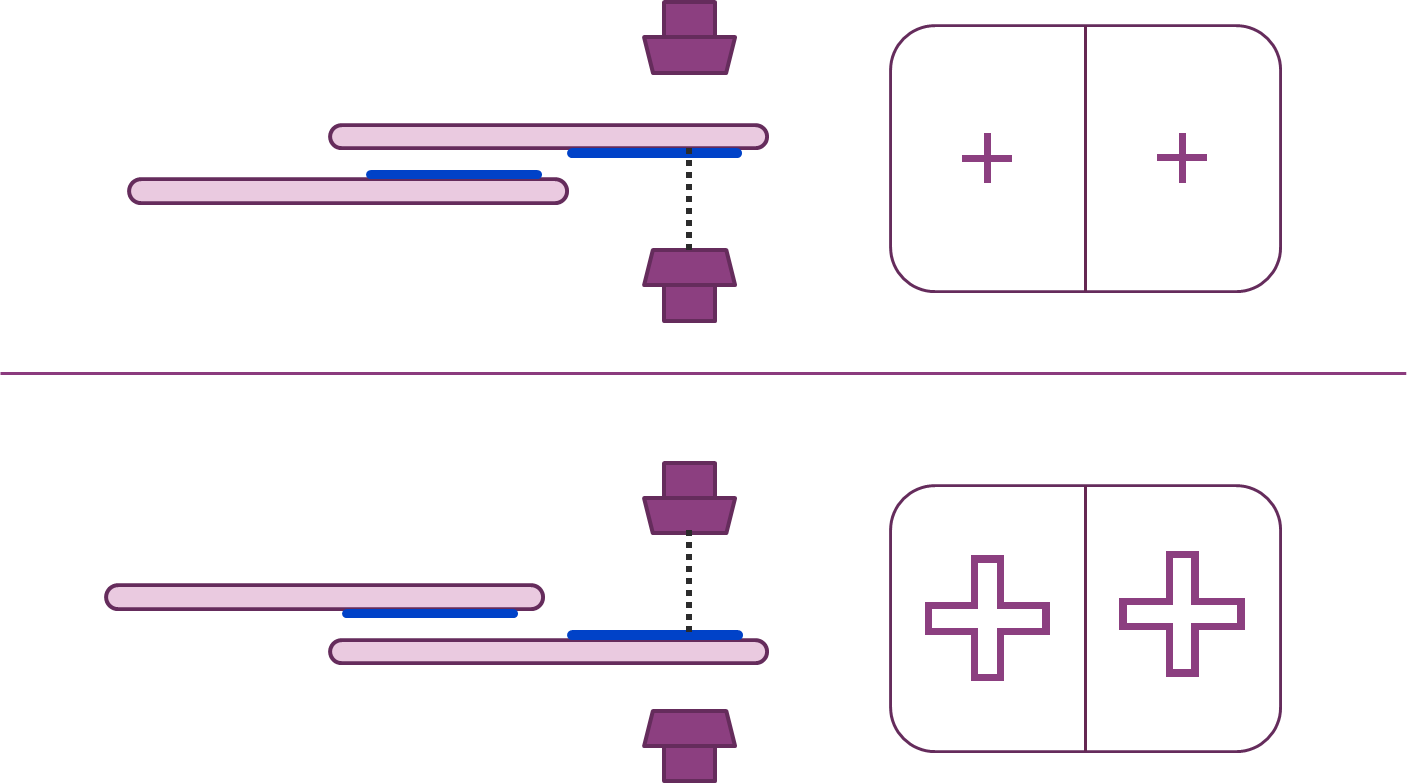

Misalignment -Compared to conventional mask-to-wafer alignment based on photolithography, wafer-to-wafer alignment is much more complicated. It requires different alignment concepts to align two processed wafers with devices. In principle, wafer-to-wafer alignment uses alignment marks on two wafers to monitor the alignment process within an alignment tool. Once two wafers are aligned, they are temporarily brought into contact; at this stage, for optical or infrared (IR) transparent wafer, the misalignment can be inspected by imaging overlay marks.

Various alignment techniques and methods have been introduced for wafer-to-wafer alignment, among which the method called SmartView [15, 16] is widely applied. Two pairs of microscopes are placed outside of the top and bottom wafers. The aligning wafers are placed “face-to-face” with a gap of less than 100 μm and vacuum-sucked on the top and bottom wafer stages, respectively. The two wafer stages can be moved back and forth horizontally. After the pair of top and bottom microscopes are aligned with each other (i.e., calibrated), the bottom wafer stage is moved in between the pairs of microscopes; the marks in the top microscopes are aligned to the alignment marks on the bottom wafer. The bottom wafer position is stored, and the bottom stage is retreated. The top wafer stage is moved to the position against the bottom microscopes. The alignment marks on the top wafer are then aligned to the bottom microscopes. The bottom wafer stage is moved back to its stored alignment position. Finally, the two aligned wafers are vertically moved to contact each other and are clamped to hold the alignment for wafer bonding, as illustrated in Figure 2. Misalignment tolerances can be achieved on the order of 0.25 μm in this method.

Figure 9.

SmartView alignment method. As 3D NAND design VIA size and pitch is scaling down to sub-micro in order to increase memory intensity, misalignment needs to be compressed down to 0.1 μm, raising a major challenge for bonding equipment suppliers. Currently main movement is striving to improve measurement repeatability and to apply feed forward method to compensate bonding misalignment.