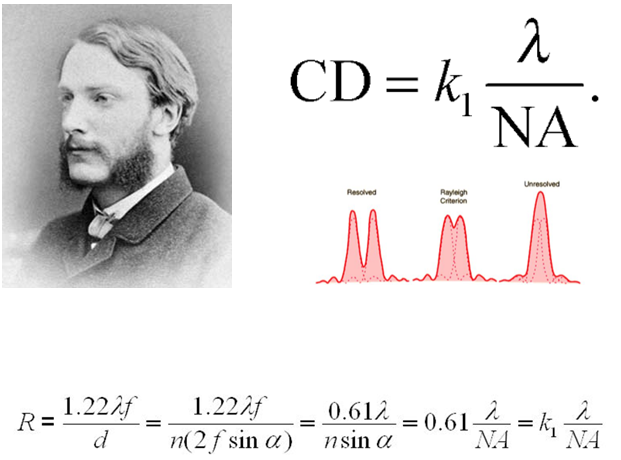

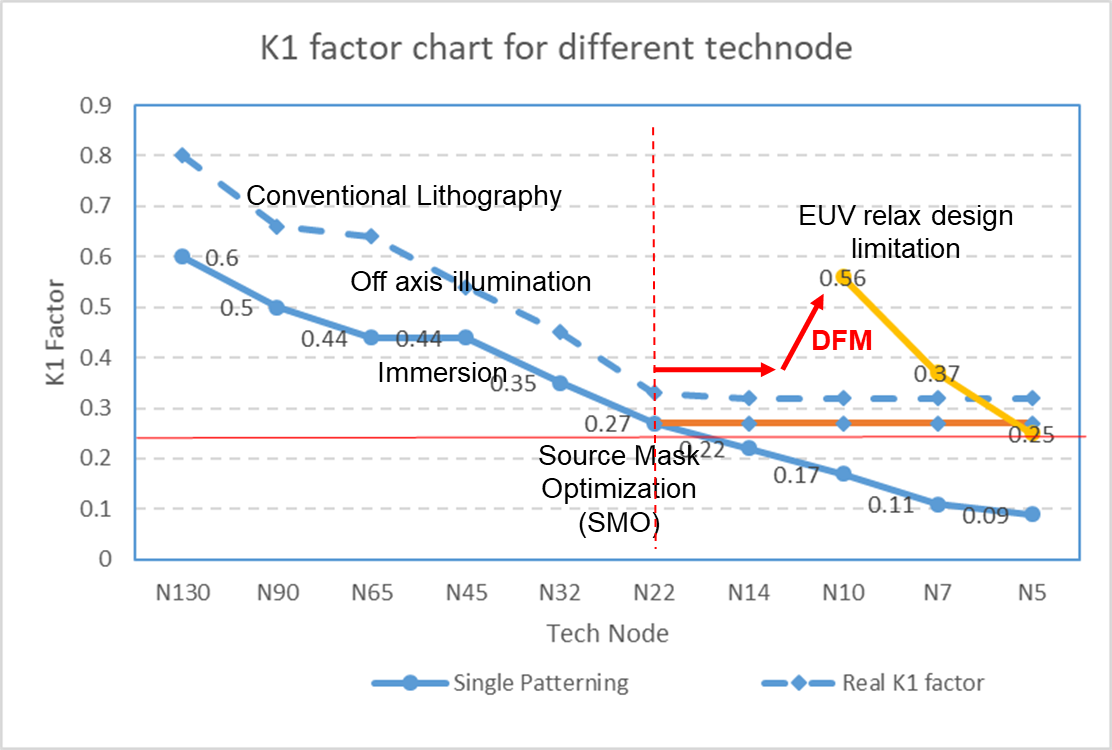

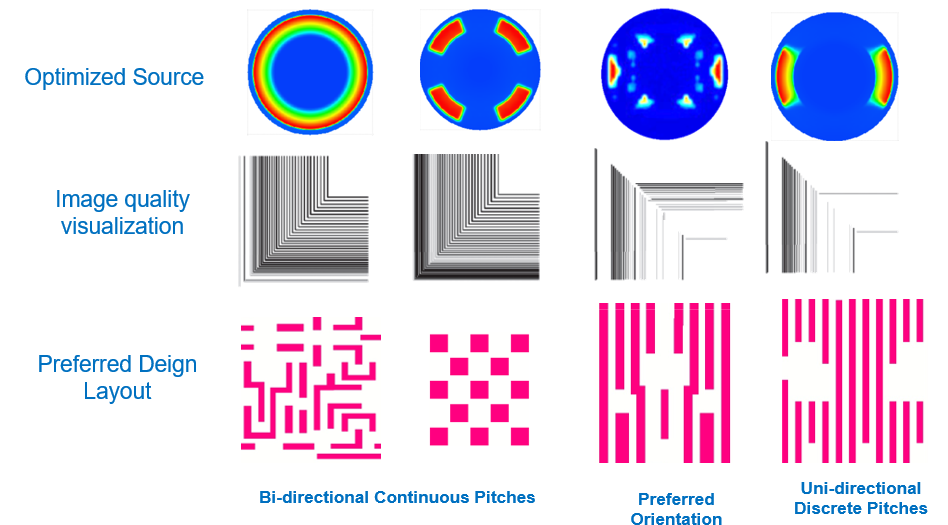

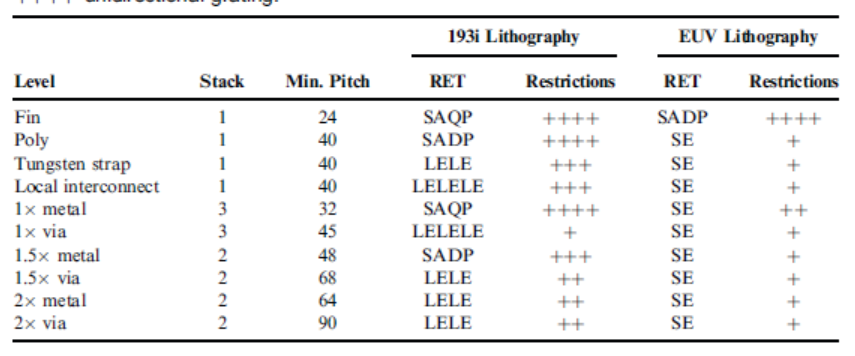

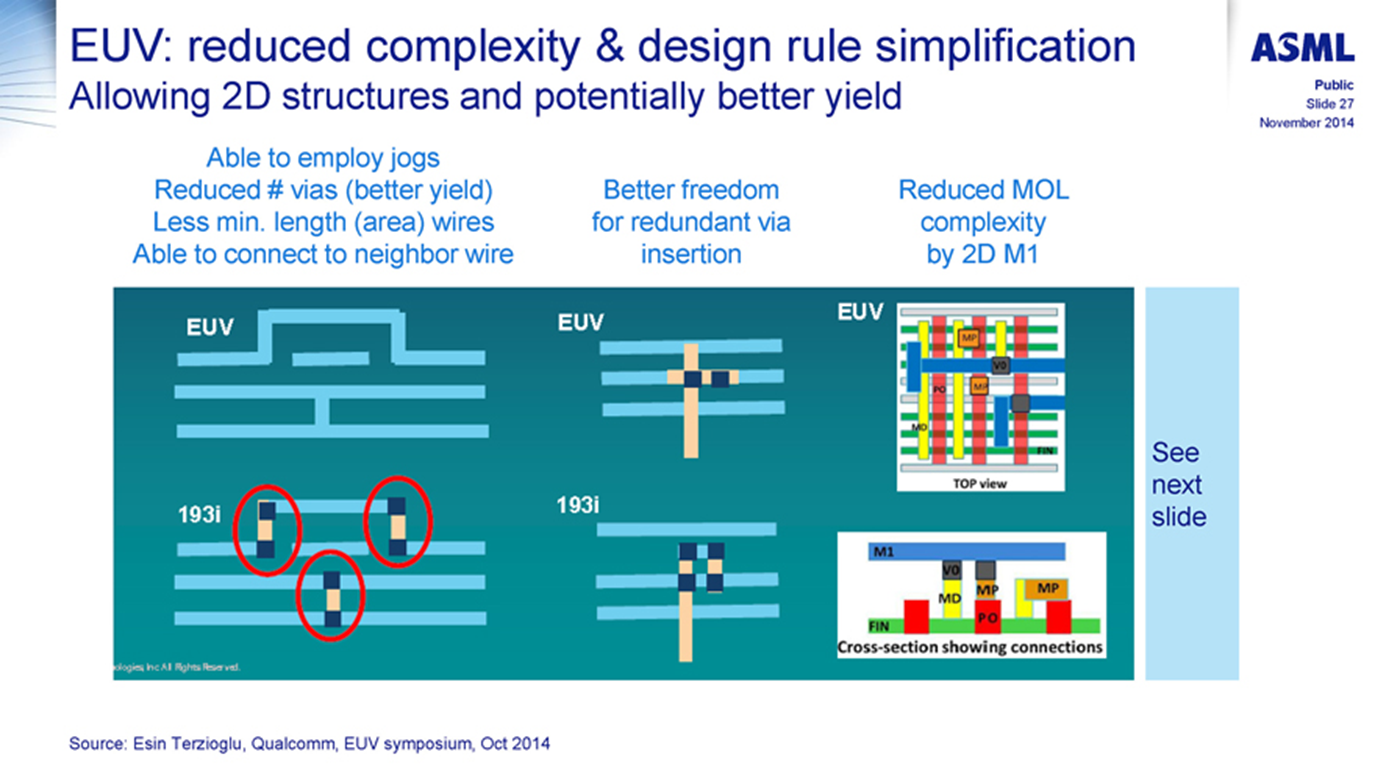

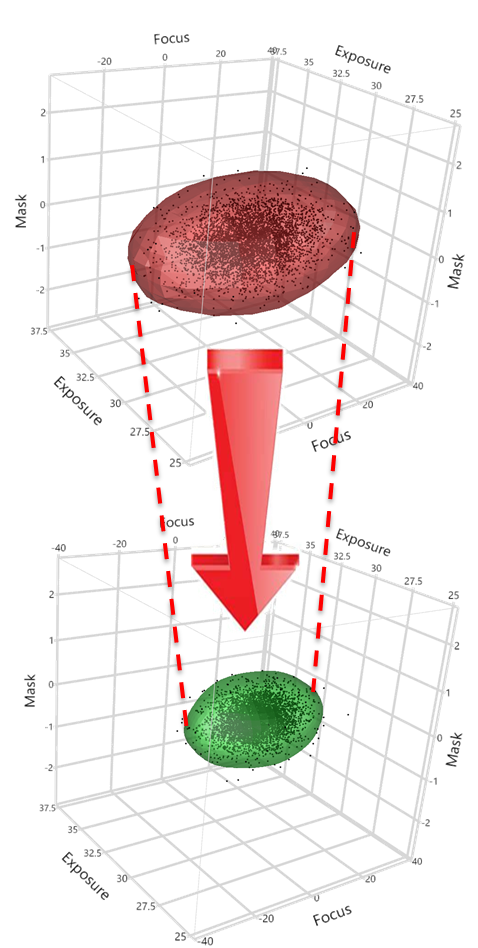

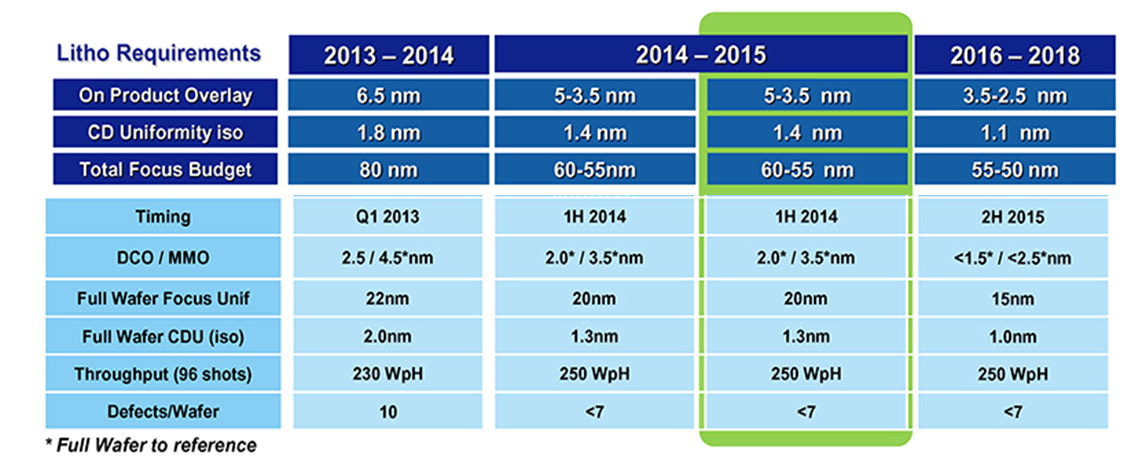

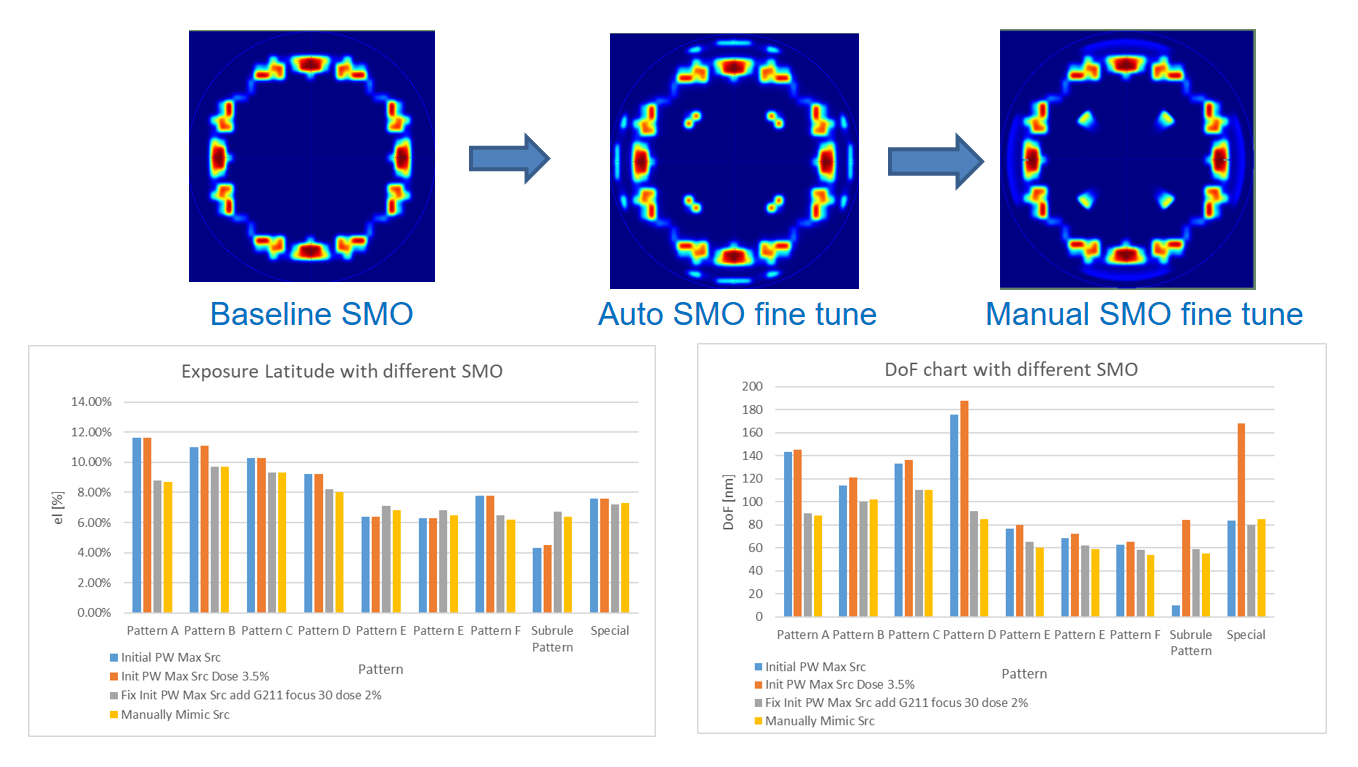

Abstract: As the IC manufacturing enter sub 20nm tech nodes, DFM become more and more important to make sure more stable yield and lower cost. However, by introducing newly designed hardware (1980i etc.) process chemical (NTD) and Control Algorithm (Focus APC) into the mature tech nodes such as 14nm/12nm, more process window and less process variations are expected for latecomer wafer fabs (Tier-2/3 companies) who just started the competition with Tier-1 companies. With improved weapons, latecomer companies are able to review their DFM strategy one more time to see whether the benefit from hardware/process/control algorithm improvement can be shared with designers. In this paper, we use OPC simulation tools from different EDA suppliers to see the feasibility of transferring the benefits of hardware/process/control algorithm improvement to more relaxed design limitation through source mask optimization (SMO): 1) Better hardware: scanner (better focus/exposure variation), CMP (intrafield topo), Mask CD variation (relaxed MEEF spec), etc. 2) New process: from positive tone development to negative tone development. 3) Better control schemes: holistic focus feedback, feedback/forward overlay control, high order CD uniformity improvement. Simulations show all those gains in hardware and process can be transferred into more relaxed design such as sub design rule structure process window include forbidden pitches (1D) and smaller E2E gaps (2D weak points).

Keywords: Design for Manufacturing (DFM); Design Friendly Manufacturing; EUV Lithography; Source Mask Optimization (SMO); Design Technology Co-optimization (DTCO); Process Window; Process Variation