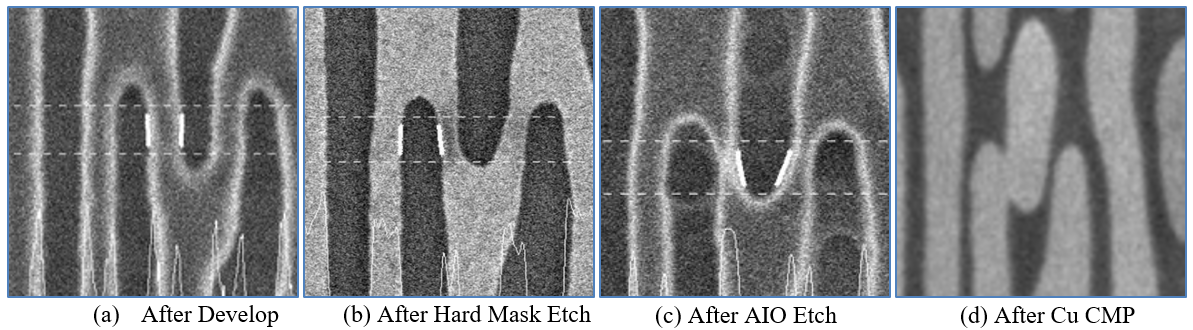

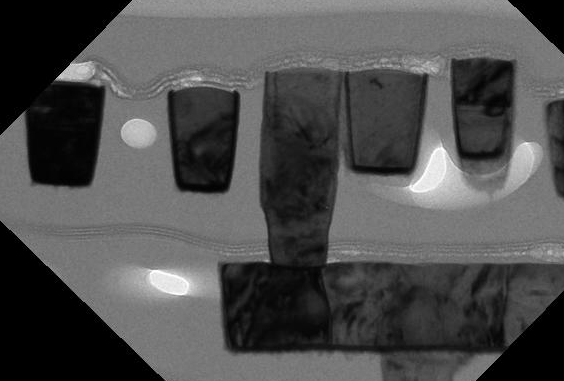

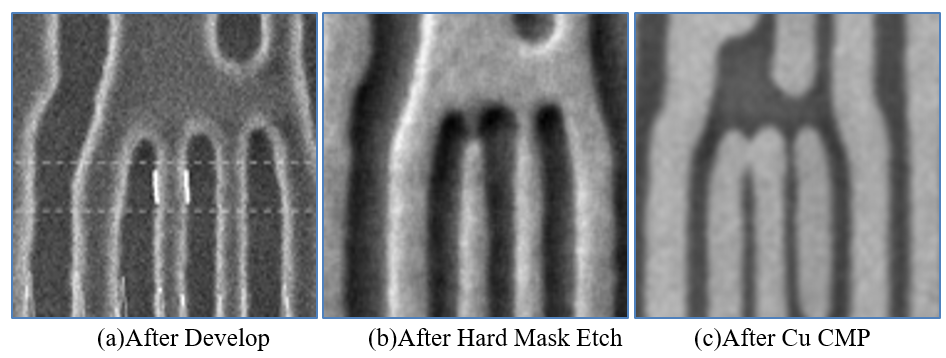

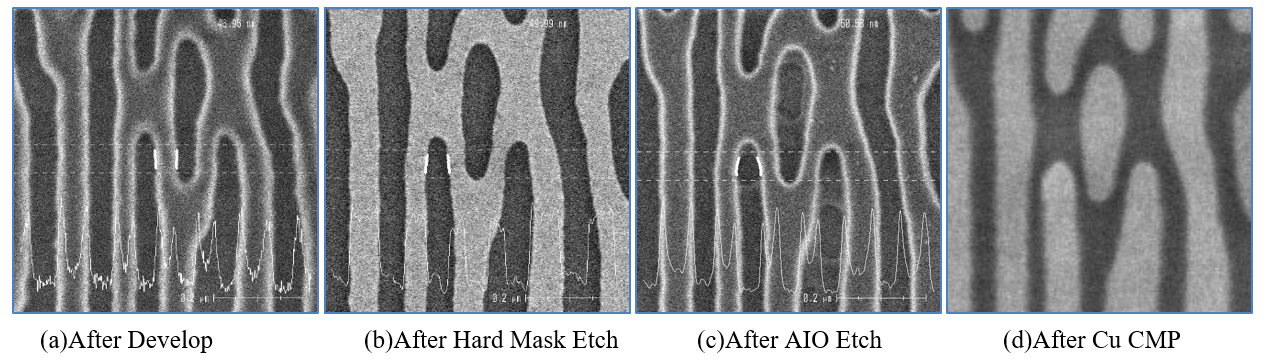

Here we will share results from the study of a 28nm device covering multiple process layers. In the case under consideration here, bridging defects were observed in the M1 process layer and were detected only after Metal Chemical-Mechanical-Planarization (Cu-CMP) process step, as shown in Figure 5(d). The conventional optical wafer inspection was set at the standard process control steps: After Develop After Hard Mask Etch After All-in-One Etch After Cu CMP, but it failed to detect any anomaly in patterning at the preceding steps. The cross-section Transmission Electron Microscopy (TEM) analysis also confirmed the bridging of the adjacent M1 lines, as shown in Figure 6. Subsequent trace back analysis by defect location, as shown in Figure 5, revealed that the pattern deformation was not sufficient at the preceding process control steps to trigger optical defect detection with Die-to-Die wafer inspection. This is a fundamental weakness of the conventional wafer inspection and review methodology.

Figure 5.

Critical defect - subtle progression through process steps. Figure 6.

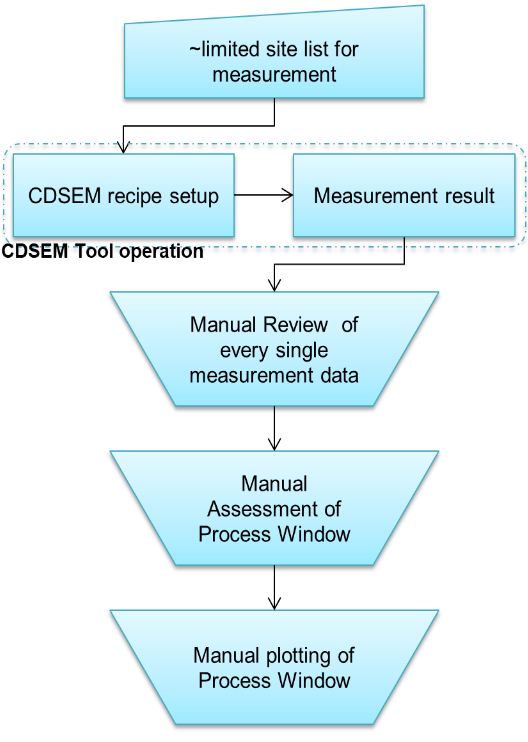

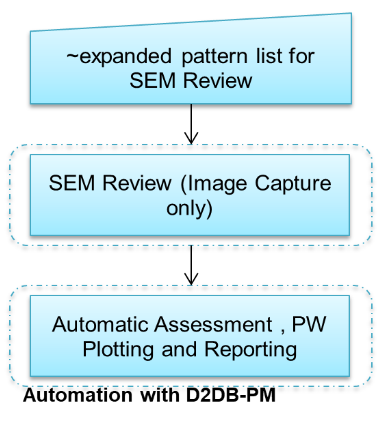

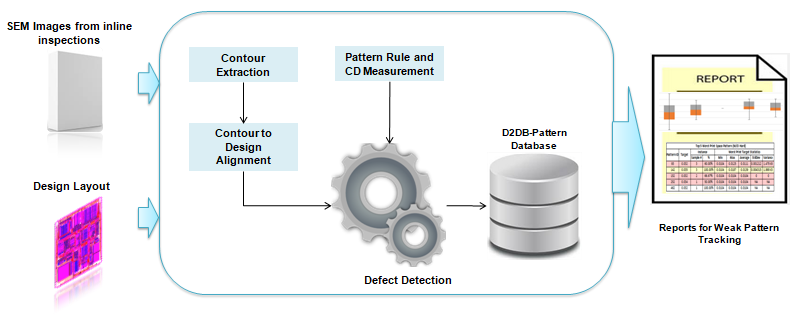

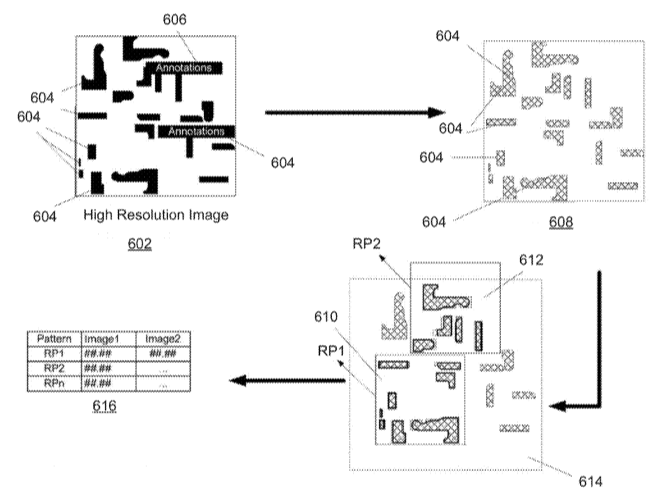

A critical defect - Cross TEM analysis of failed sample. In addition to the need to improve defect detection there was a requirement for expanding the sample size for the measurement of critical dimensions for determining a more accurate process window. So it was decided to apply the D2DB-PM solution to perform root cause study from the lithography step to the final metal fill and CMP process steps using a process window qualification (PWQ) wafer. The potential to run fully automated analysis of SEM Review images offered an opportunity to collect a huge volume of images from the wafer– which is otherwise impractical to do on a CDSEM platform. With a combination of inputs from OPC verification results and the PWQ optical wafer inspection, a set of about 200 die locations were shortlisted for SEM review across and beyond the process window die. The data flow outlined in Figure 3 was employed by the team for automatically processing the thousands of SEM images that were collected after every process step. The automated D2DB-PM solution measured the feature size of all patterns-of-interest falling within the field of view of every SEM image. A CD error threshold was then specified by the user to define the process window – such that die in which the errors of all measured patterns fell in the range of the threshold were used to define the process window.

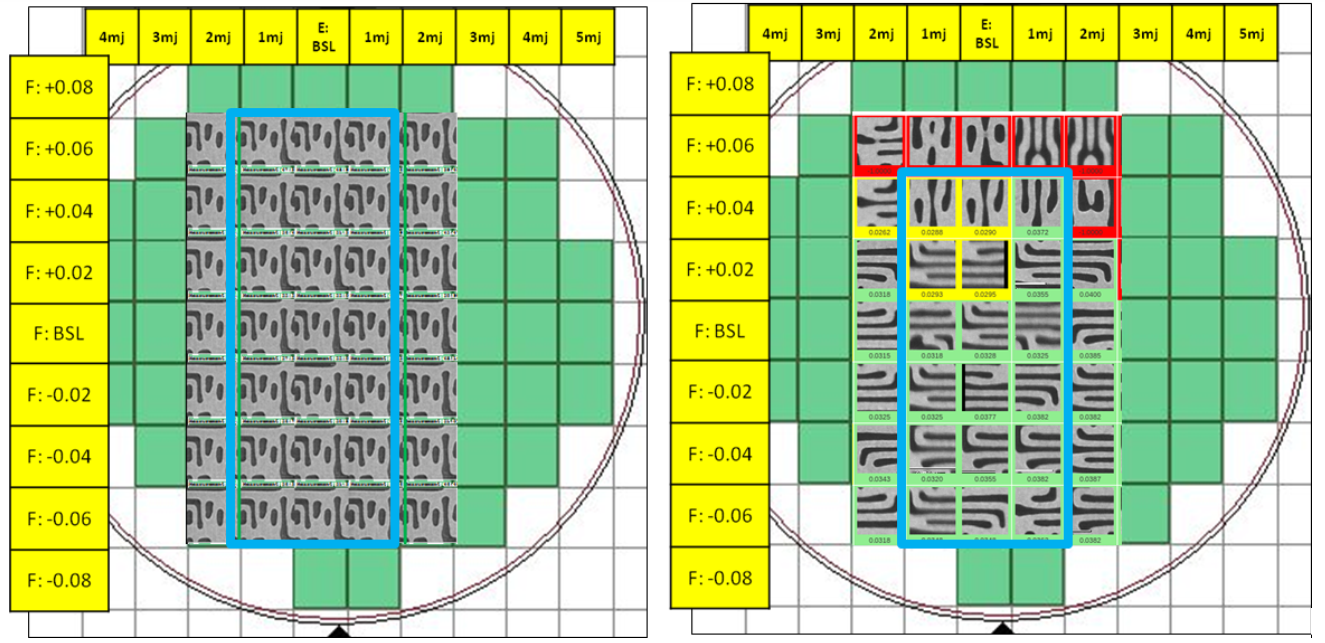

Figure 7.

Process Window determination: (Left) By conventional CDSEM (Right) By D2DB-PM. In Figure 7, the blue rectangle represents the process window obtained by the conventional method using CDSEM (left side) and by the D2DB-PM solution (right side). The conventional CDSEM measurement is done on 10 sites in each die with manual data analysis whereas the D2DB-PM measurement is done on over 100 sites in each of the 200 SEM images from each dice processed automatically. Additionally, based on certain user defined criteria a classification is assigned for (1) safe patterns within process window – green border, (2) marginal patterns with soft defects – yellow border, and (3) failed patterns just outside the process window region – red border. This color-coded process window map along with the CD values of target features is stored in the report.

In addition to finding a more accurate process window at every patterning step, a number of failing patterns were also found that showed a clear defect progression across fabrication processes, as shown in Figure 8.

Figure 8.

Example of pattern defect detected by D2DB-Pattern Monitor solution. As a result of the vast amount of feature size and defect information collected and processed, feedback was provided to the design and OPC control teams. They updated the key impacted features and provided an improved version of the reticle. Validation of the revised reticle was also done using the same D2DB-PM methodology and confirmed that the known failing patterns were fixed and that the process window had been improved. An example of a process problem that was originally detected is shown in Figure 5, and its confirmed fix is shown in Figure 9.

Figure 9.

Example of monitoring after process fix