In 1998, S. Kuiper introduced the discovery that for pores smaller than 1 um, the pressure build-up due to hydrogen gas formation can be large enough to cause rupture of the membrane during the positive structure release by KOH etching

[12] ,[13]. However, till now there are no reports that can describe the exact mechanism behind this phenomenon.

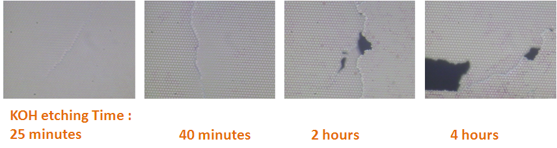

In order to explore the intrinsic mechanism, we have been doing a considerable amount of experimental works. For 500 um thick wafers it’s impossible to finish corrosion in short times, however we found rupture of the sieve units, with (100) wafer, shown as Figure 4. It is highly likely that the rupture happens during the wet etching though the pores.

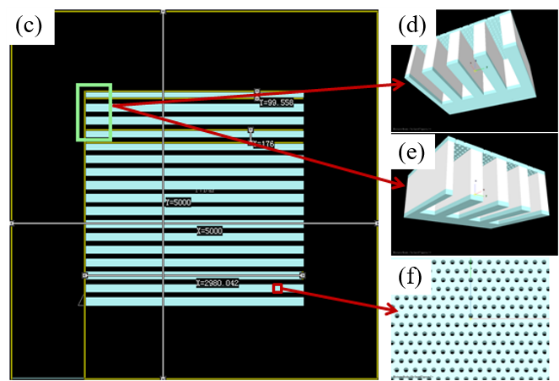

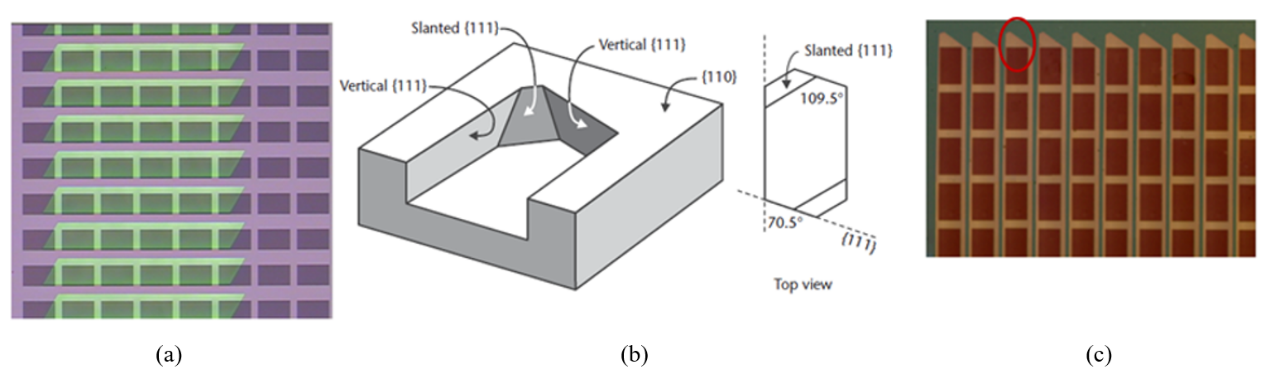

There is one hypothesis assuming that it’s hydrogen bubbles rupturing the upper layer, however we see little support to this assumption. With 0.45 um diameter cylindrical holes in LPCVD silicon nitride layer as hard mask at the front side, the KOH Etching of (100) Si will be self-terminated in several minutes, therefore it’s so questionable that how the hydrogen bubbles could create cracks to the filtration structure if hydrogen bubble just adsorbs the wet etching surface, as shown in Figure 5.

Figure 5.

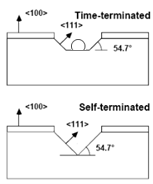

KOH Etching of (100) Si wafer. A variety of theories have been formulated to explain the irradiation damage due to implanted ions in metals which is mainly related to the nuclear reactor technology. So far, an especially elegant procedure has been suggested by Bruel and termed Smart-Cut. It is based on the hydrogen implantation before bonding which leads to the splitting of silicon wafers along hydrogen-filled micro-cracks, and the cracks are induced by the precipitation of the implanted hydrogen during a heating step after bonding. When temperature changes, material mismatch may cause defect growth such as cavities which generate lot of stresses at the interface. It is also the only mechanism by which the thermal mismatch plays a role in wafer splitting in the Smart-Cut process. As the KOH etching is an exothermic process, the hydrogen is not gathering on the wet etching surface but rather diffuses along the interface between Si and LPSiN layer

[24].

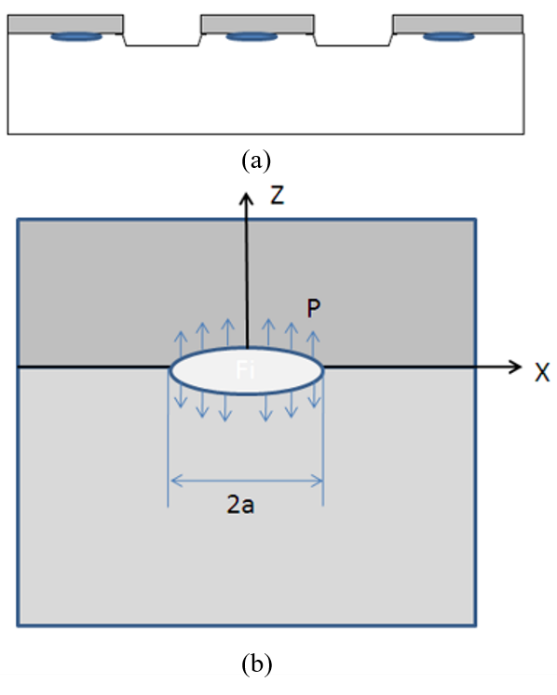

As showed in Figure 6, with a uniform pressure loading over the entire bubble surface inside, the stress will induce cleavage at the interface. As the sieving layer contains a periodic array of holes, hydrogen bubbles are distributed in the interface of Si and LPSiN layer. As hydrogen molecules are gathering, cracks in the filtration membrane will occur when the shear force per unit rises to the maximum stress that the LPSiN film can withstand.

Figure 6.

Crack model of a periodic array with hydrogen bubble distributed in the interface of Si and LPSiN layer, (b) the crack configuration of the fracture mechanics model. 2.2.2.2. Special Care to Protect the Front Side against KOH Solution

Although the theory remains to be studied, we try to solve the problem. SF

6/O

2 plasma dry etching from the front side of the wafer through the pores was employed

[12] ,[13]. However, SF

6/O

2 plasma does not perform enough lateral etch (undercut) of the silicon to connect the trenches. And the silicon nitride exhibits a poor etch resistance to the plasma and as a result at room temperature the membrane shows a significant under-etch. As the apparatus is a single wafer etcher and the whole process takes about one hour, this method is super time-consuming.

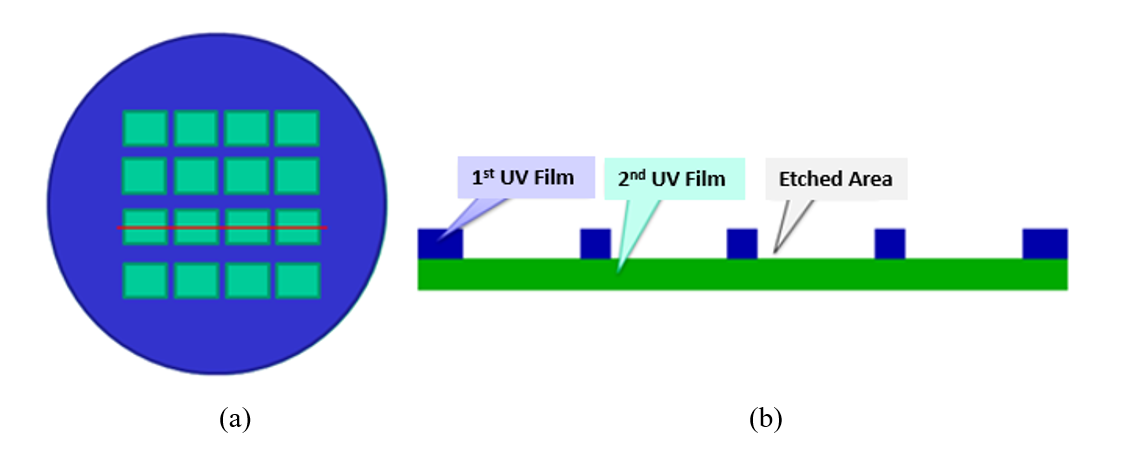

An idea to ensure a reasonable fabrication yield was employed, in which special care was taken to protect the front side against the KOH solution

[14]. Black wax and polymer coat were implemented as a protective coating for KOH etching. However, after dissolution of wax in toluene solvent there is still residual of black wax, which is not acceptable for operating products. By using a polymer coat to mount the sample to a glass and black wax to seal the sample and the glass, we only obtained a fabrication yield of 31%. Actually we tried AR-PC 504 on sieving layer side of wafers against wet etching processes, but failed as the resist layer peels off in lessthan one hours from the substrate in 33% KOH solution and at 80℃ temperature. Therefore it would be worthy trying to attack the wet etching problems from a different perspective.

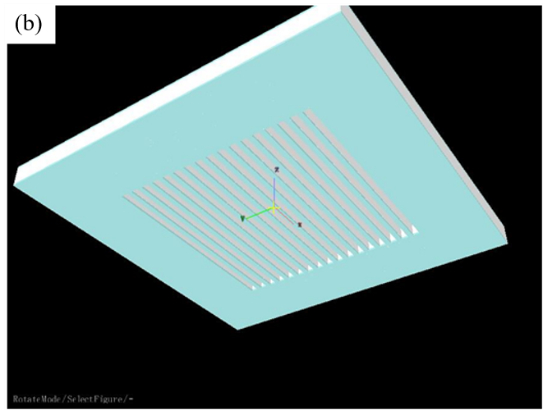

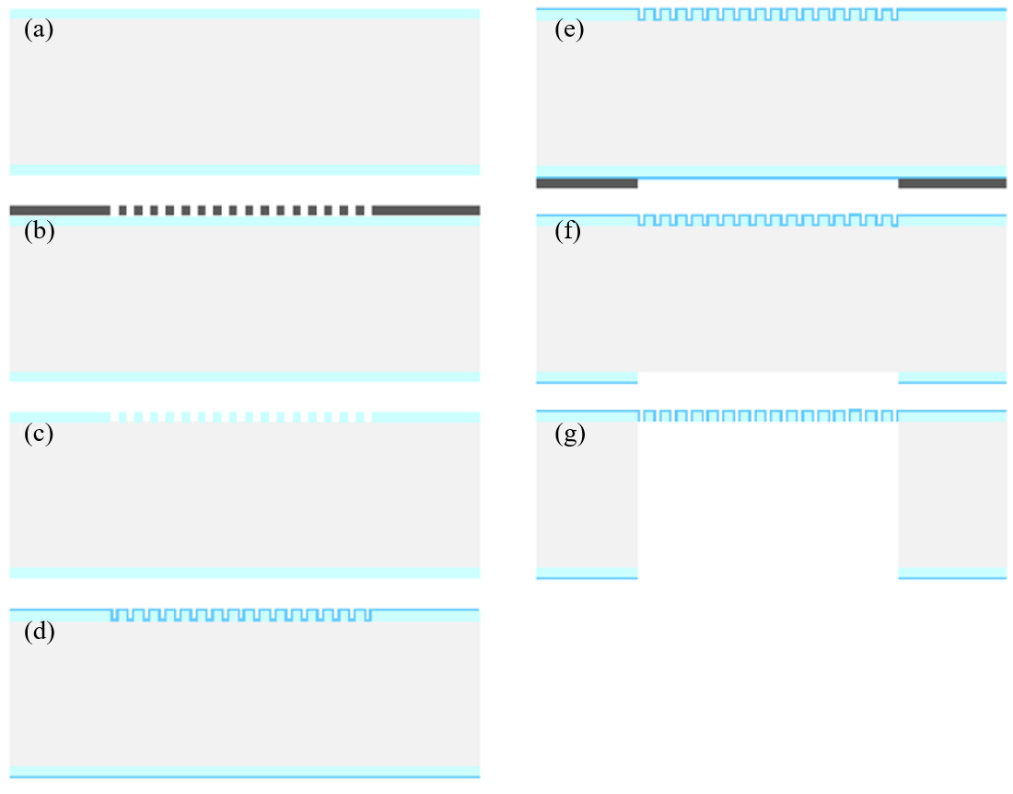

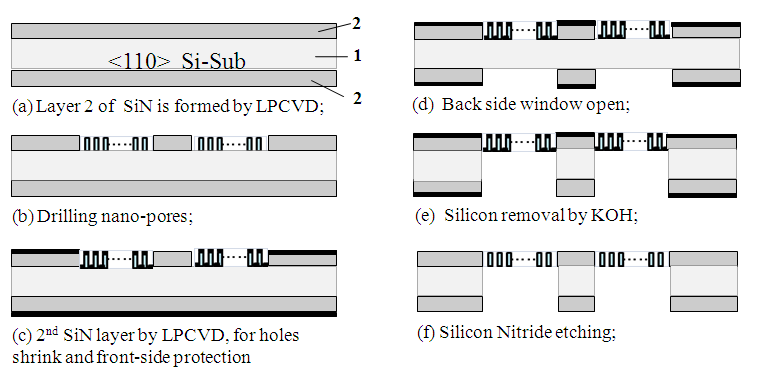

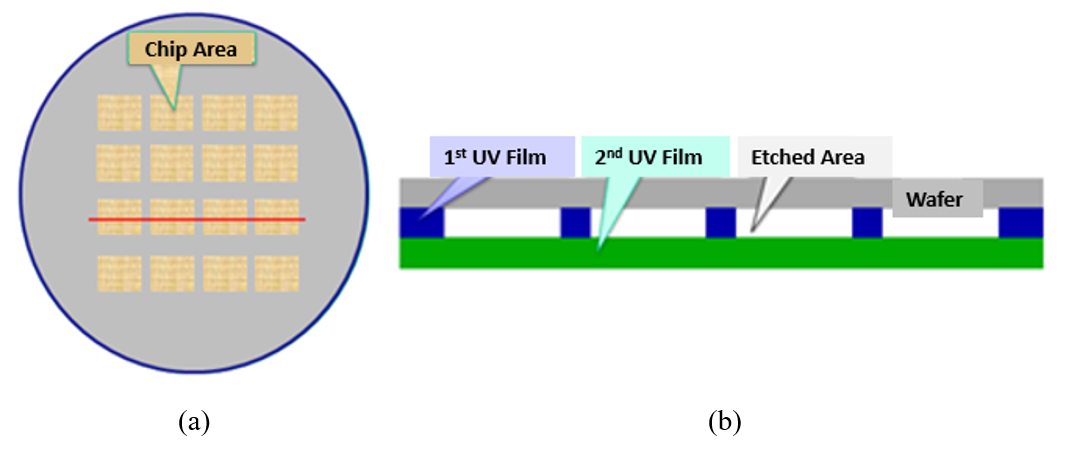

Fortunately, we eventually achieved a reliable front side protection against KOH etching through the pores. We improved the frication process shown in Figure 2 by depositing a 2nd 200 Å thick thin layer of high stress SiN by LPCVD to both sides, which will effectively prevent the front side from KOH etching in case of hydrogen gas induced rupture build-up during wet etching, as shown in Figure 7. The 200 Å thick SiN at the bottom of the holes will automatically break easily and fall off when the silicon beneath is etched by KOH. As a result we achieved much improved yield results.

Figure 7.

Improved fabrication process with special care of front side against KOH etching.